# **Laboratory 1**

(Due date: 005: February 1st, 006: February 2nd)

## **OBJECTIVES**

- ✓ Implement a Digital System: Control Unit and Datapath Unit.

- ✓ Describe Algorithmic State Machine (ASM) charts in VHDL.

- ✓ Learn the basics of Microprocessor Design.

## **VHDL CODING**

✓ Refer to the <u>Tutorial: VHDL for FPGAs</u> for parametric code for: Register and ALU.

# FIRST ACTIVITY: DESIGN OF A SMALL MICROPROCESSOR (70/100)

#### **DESIGN PROBLEM**

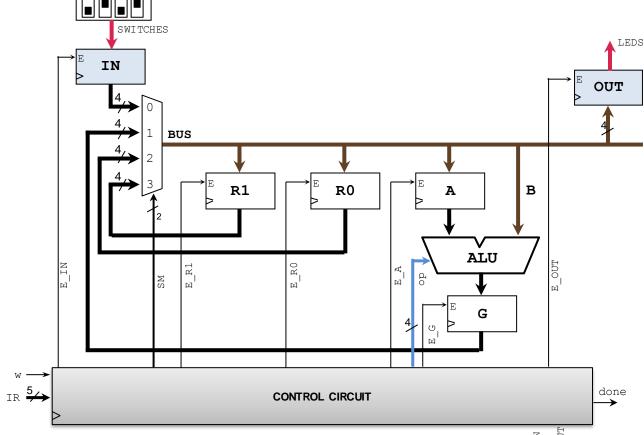

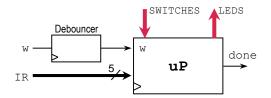

• Implement the following 4-bit microprocessor:

- Control Circuit:

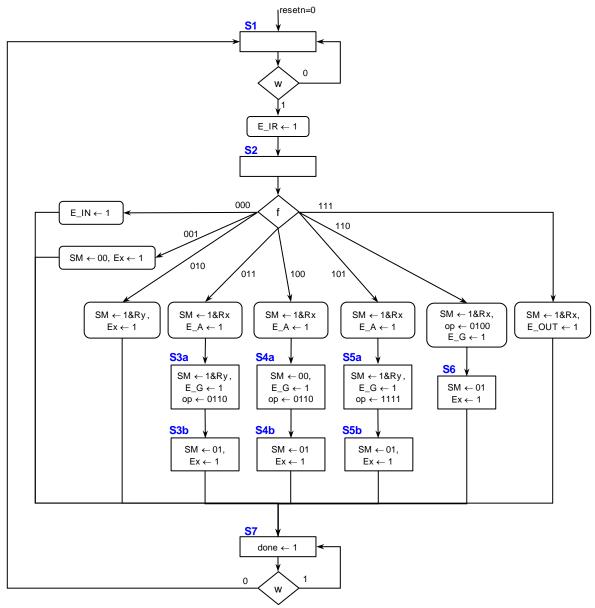

- ✓ The 5-bit instruction, provided by IR, is captured by the control circuit when w=1. The instruction is then processed, and it finishes when done is asserted. A new instruction can then be provided in the next clock cycle.

#### Instruction Set:

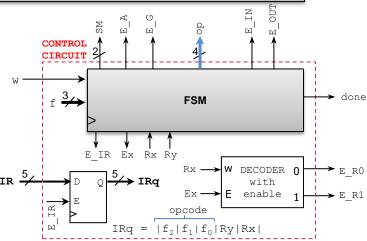

✓ Instruction: |f<sub>2</sub>|f<sub>1</sub>|f<sub>0</sub>|Ry|Rx|

| F   | Operation    | Function                 |  |  |

|-----|--------------|--------------------------|--|--|

| 000 | load IN      | $IN \leftarrow Switches$ |  |  |

| 001 | load Rx, IN  | Rx ← IN                  |  |  |

| 010 | copy Rx, Ry  | Rx ← Ry                  |  |  |

| 011 | add Rx, Ry   | Rx ← Rx + Ry             |  |  |

| 100 | add Rx, IN   | $Rx \leftarrow Rx + IN$  |  |  |

| 101 | xnor Rx, Ry  | Rx ← Rx XNOR Ry          |  |  |

| 110 | inc Rx       | $Rx \leftarrow Rx + 1$   |  |  |

| 111 | load OUT, Rx | OUT ← Rx                 |  |  |

### ✓ Instruction examples:

$^{\circ}$  load R1, IN  $\equiv$  IR = 001X1  $^{\circ}$  add R0, R1  $\equiv$  IR = 01110

#### Control Circuit: FSM

Arithmetic Logic Unit (ALU):

| sel  | Operation     | Function              | Unit             |

|------|---------------|-----------------------|------------------|

| 0000 | y <= A        | Transfer 'A'          |                  |

| 0001 | y <= A + 1    | Increment 'A'         |                  |

| 0010 | y <= A - 1    | Decrement 'A'         |                  |

| 0011 | y <= B        | Transfer <b>\</b> B'  | A with me at i a |

| 0100 | y <= B + 1    | Increment 'B'         | Arithmetic       |

| 0101 | y <= B - 1    | Decrement 'B'         |                  |

| 0110 | y <= A + B    | Add 'A' and 'B'       |                  |

| 0111 | y <= A - B    | Subtract 'B' from 'A' |                  |

| 1000 | y <= not A    | Complement 'A'        |                  |

| 1001 | y <= not B    | Complement 'B'        |                  |

| 1010 | y <= A AND B  | AND                   |                  |

| 1011 | y <= A OR B   | OR                    | 1:-              |

| 1100 | y <= A NAND B | NAND                  | Logic            |

| 1101 | y <= A NOR B  | NOR                   |                  |

| 1110 | y <= A XOR B  | XOR                   |                  |

| 1111 | y <= A XNOR B | XNOR                  |                  |

#### **PROCEDURE**

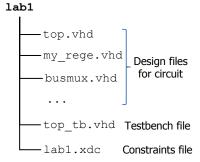

- Vivado: Complete the following steps:

- ✓ Create a new Vivado project. Select the corresponding Artix-7 FPGA device (e.g.: the XC7A50T-1CSG324 FPGA device for the Nexys A7-50T board).

- ✓ Write the VHDL code for the given circuit. Synthesize your circuit to clear syntax errors.

- Suggestion: Use the Structural Description: Create a separate .vhd file for the components (register, ALU, MUX, Control Circuit) and interconnect them all in a top file. The Control Circuit and ALU have their own components.

- ✓ Write the VHDL testbench to simulate your circuit.

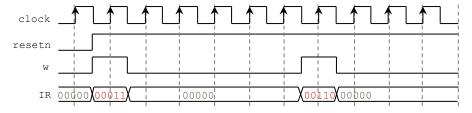

- Your testbench must test the following Assembly program (use a 100 MHz input clock with 50% duty cycle):

```

load IN; IN \leftarrow 0110 (SWs = 0110) load R0, IN; R0 \leftarrow 0110 copy R1, R0; R1 \leftarrow 0110, R0 \leftarrow 0110 inc R0; R0 \leftarrow 0111 add R1, R0; R1 \leftarrow 0111 + 0110 = 1101 xnor R1, R0; R1 \leftarrow 1101 xnor 0111 = 0101 load OUT, R1; OUT \leftarrow 0101

```

• This timing diagram depicts an example where two instructions are loaded.

- Perform <u>Behavioral Simulation</u> and <u>Timing Simulation</u> of your design. **Demonstrate this to your TA**.

- Behavioral Simulation: To help debug your circuit, add internal signals (e.g.: state, R0, R1, A) to the waveform view.

- $\checkmark$  I/O Assignment: Create the XDC file associated with your board.

- Suggestion (Nexys A7-50T/A7-100T, Nexys 4/DDR):

| Board pin names      | CLK100MHZ | CPU_RESET | SW8-SW5 | SW4-SW0 | BTNC | LED4 | LED3-LED0 |

|----------------------|-----------|-----------|---------|---------|------|------|-----------|

| Signal names in code | clock     | resetn    | IN      | IR      | W    | done | OUT       |

- Note: synchronous circuits always require a clock and reset signal.

- **Reset signal**: As a convention in this class, we use active-low reset (*resetn*). Thus, we tie *resetn* to the active-low push button CPU RESET of the Nexys A7-50T/A7-100T, Nexys 4/DDR board.

- **Clock signal**: Like other signals in the XDC file, uncomment the lines associated with the clock signal and replace the signal label with the name used in your code. In addition, there is parameter <code>-period</code> that is set by default to 10.00. This is the period (in ns) that your circuit should support.

# SECOND ACTIVITY: TESTING (30/100)

- In order to properly test the microprocessor, we need the avoid mechanical bouncing on the pushbutton for input w. Connect the debouncer circuit (use the given files: mydebouncer.vhd, my genpulse sclr.vhd) on the input w.

- Note that you do not need to simulate the circuit that includes the debouncer.

- ✓ Generate and download the bitstream on the FPGA and test the Assembly Program. **Demonstrate this to your TA**.

- □ To test the Assembly program, load each instruction via the input IR and use the input W to feed the instruction.

#### **SUBMISSION**

- Submit to Moodle (an assignment will be created):

- ✓ This lab sheet (<u>as a .pdf</u>) completed and signed off by the TA (or instructor).

- ✓ (As a .zip file) All the generated files: VHDL code, VHDL testbench (for the uP block), and XDC file. DO NOT submit the whole Vivado Project.

- Your .zip file should only include one folder. Do not include subdirectories.

- It is strongly recommended that all your design files, testbench, and constraints file be located in a single directory. This will allow for a smooth experience with Vivado.

- You should only submit your source files AFTER you have demoed your work.

Submission of work files without demoing will be assigned <u>NO CREDIT</u>.

| TA signature: | Date: |

|---------------|-------|

|               |       |